## AB1 PROTOTYPING BOARD USER'S GUIDE

## 1.0. Summary

The AB1 prototyping board provides a 3 x 3.75" prototyping area (0.1" center through-hole) with access to all MCU I/O signals. Access to I/O signals is provided by a 96-pin, high density connector that mates directly to the expansion connector of C8051F020-TB, C8051F040-TB, C8051F060-TB, and C8051F120-TB target boards. A 128 kB SRAM is installed on the board which can be connected to the MCU's External Memory Interface by installing a single 2-pin jumper (included).

#### 2.0 Features

- 96 pin 3 row connector

- 128 kB SRAM Part number IDT71V124

- SRAM disable jumper J1(open = disabled, closed = enabled)

- · Duplicate of connector pins for easy access to signals

- · Digital and analog supply and ground rails

## 3.0 SRAM Details

The IDT71V124SA12PH is a high-speed with 12 nanosecond access and cycle time static SRAM. For more further information on access and cycle times for this SRAM please refer to the IDT71V124 data sheet available at <a href="http://www.idt.com/docs/71V124SA">http://www.idt.com/docs/71V124SA</a> DS 30147.pdf. To enable the SRAM jumper J1 must be installed and the /CS Chip Select pin must be pulled low. The SRAM utilizes the External Memory Interface from F02X and later devices, more information on using this interface can be found in Section 16 of the C8051F02x Data Sheet. When enabled the SRAM uses ports 5, 6, and 7 and the upper nibble of port 4. The pin-out is as follows:

| Signal Name | SRAM Pin(s)             | C8051F02XTB<br>Connection | Description           |

|-------------|-------------------------|---------------------------|-----------------------|

| /WE         | 12                      | P4.7                      | Write Enable          |

| /CS         | 5                       | P4.4(J1 closed)           | Chip Select           |

| /OE         | 28                      | P4.6                      | Output Enable         |

| VDD         | 8,24                    | +3 VD                     | Digital Power         |

| GND         | 9,25                    | GND                       | Digital Ground        |

| I/O0I/O7    | 6,7,10,11,22,23,26,27   | P7.0P7.7                  | Data Bus              |

| A0A7        | 1,2,3,4,13,14,15,16     | P6.0P6.7                  | Address Bus Low Byte  |

| A8A15       | 17,18,19,20,21,29,30,31 | P5.0P5.7                  | Address Bus High Byte |

| A16         | 32                      | P4.5                      | Bank Select           |

# 4.0 Hardware Setup

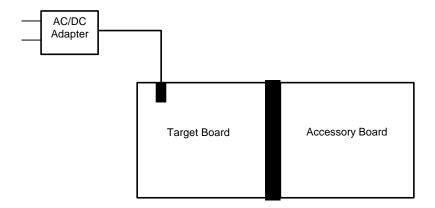

A compatible target board is connected to the accessory board as shown in Figure 1.

Figure 1. Hardware Setup

2 Rev. 0.3

Notes:

# **AN171**

### **Contact Information**

Silicon Laboratories Inc. 4635 Boston Lane Austin, TX 78735 Tel: 1+(512) 416-8500

Fax: 1+(512) 416-9669 Toll Free: 1+(877) 444-3032 Email: productinfo@silabs.com Internet: www.silabs.com

The information in this document is believed to be accurate in all respects at the time of publication but is subject to change without notice. Silicon Laboratories assumes no responsibility for errors and omissions, and disclaims responsibility for any consequences resulting from the use of information included herein. Additionally, Silicon Laboratories assumes no responsibility for the functioning of undescribed features or parameters. Silicon Laboratories reserves the right to make changes without further notice. Silicon Laboratories makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Silicon Laboratories assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. Silicon Laboratories products are not designed, intended, or authorized for use in applications intended to support or sustain life, or for any other application in which the failure of the Silicon Laboratories product could create a situation where personal injury or death may occur. Should Buyer purchase or use Silicon Laboratories products for any such unintended or unauthorized application, Buyer shall indemnify and hold Silicon Laboratories harmless against all claims and damages.

Silicon Laboratories and Silicon Labs are trademarks of Silicon Laboratories Inc.

Other products or brandnames mentioned herein are trademarks or registered trademarks of their respective holders.